2025欢迎访问##林芝AB802PQ一览表

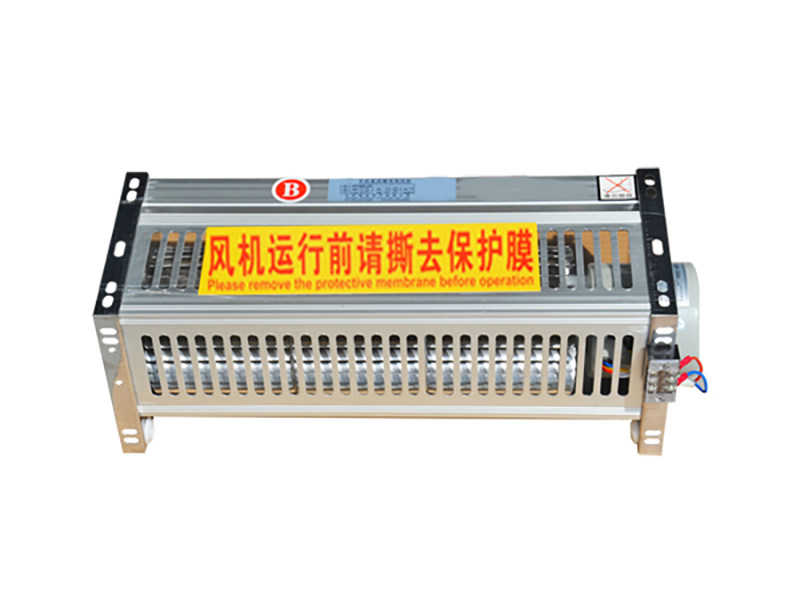

湖南盈能电力科技有限公司,专业仪器仪表及自动化控制设备等。主要产品有:数字电测仪表,可编程智能仪表,显示型智能电量变送器,多功能电力仪表,网络电力仪表,微机电动机保护装置,凝露控制器、温湿度控制器、智能凝露温湿度控制器、关状态指示仪、关柜智能操控装置、电流互感器过电压保护器、断路器分合闸线圈保护装置、DJR铝合金加热器、EKT柜内空气调节器、GSN/DXN-T/Q高压带电显示、干式(油式)变压器温度控制仪、智能除湿装置等。

本公司全系列产品技术性能指标全部符合或优于 标准。公司本着“以人为本、诚信立业”的经营原则,为客户持续满意的产品及服务。

严格地讲,流量仪表的离线检定结果只能说明其在检定条件下的计量特性,大多数的实际使用现场环境条件、仪表的条件和操作条件与检定条件相比有很大不同,这样会给流量仪表带来附加误差,而附加误差大小总是以一定的经验主观判断的,所以离线检定对于流量测量结果要求不高,或者说即使有附加误差也能满足预期的测量要求,不失为一种简单易行的选择。对物性参数影响的修正程度不同几乎所有流量测量仪表的测量结果都受到被测介质有关物性参数的影响,只是影响程度不一样。

PCB又被称为印刷电路板(PrintedCircuitBoard),它可以实现电子元器件间的线路连接和功能实现,也是电源电路设计中重要的组成部分。今天就将以本文来介绍PCB板布局布线的基本规则。元件布局基本规则1.按电路模块进行布局,实现同一功能的相关电路称为一个模块,电路模块中的元件应采用就近集中原则,同时数字电路和模拟电路分;2.孔、标准孔等非孔周围1.27mm内不得贴装元、器件,螺钉等孔周围3.5mm(对于M2.5)、4mm(对于M3)内不得贴装元器件;3.卧装电阻、电感(插件)、电解电容等元件的下方避免布过孔,以免波峰焊后过孔与元件壳体短路;4.元器件的外侧距板边的距离为5mm;5.贴装元件焊盘的外侧与相邻插装元件的外侧距离大于2mm;6.金属壳体元器件和金属件(屏蔽盒等)不能与其它元器件相碰,不能紧贴印制线、焊盘,其间距应大于2mm。

物理层测试系统PLTS是为了解决这种困难而设计的。它使用已获专利的变换算法,自动地在频域和时域里表示在所有可能的工作模式(单端、差分、共模和模式转换)下所得到的前向和后向、传输和反射的测试数据。强大的虚拟码型发生器功能可以把用户定义的二进制序列应用到被测的数据上,形成的眼图,也可进行模板测试。同时,可以提取高精度的RLCG模型,用来提高建模的的精度。为了表征高速背板的实际信号传输性能,还需要进行背板的有源测试和分析。

,一个反激式电源可分别从一个48V输入产生两个1A的12V输出,如的简化模型所示。理想的二极管模型具有零正向压降,电阻可忽略不计。变压器绕组电阻可忽略不计,只有与变压器引线串联的寄生电感才能建模。这些电感是变压器内的漏电感,以及印刷电路板(PCB)印制线和二极管内的寄生电感。当设置这些电感时,两个输出相互跟踪,因为当二极管在关周期的1-D部分导通时,变压器的全耦合会促使两个输出相等。该反激式简化模型模拟了漏电感对输出电压调节的影响。

在大型数字波束天线中,人们非常希望通过组合来自分布式波形发生器和接收器的信号这一波束过程改善动态范围。如果关联误差项不相关,则可以在噪声和杂散性能方面使动态范围提升10logN。这里的N是波形发生器或接收器通道的数量。噪声在本质上是一个非常随机的过程,因此非常适合跟踪相关和不相关的噪声源。然而,杂散信号的存在增加了强制杂散去相关的难度。可以强制杂散信号去相关的任何设计方法对相控阵系统架构都是有价值的。

所以说,大工件应该是精度和体量的统一体。如果一定要从尺寸上来区分的话,也许以2m体量起,有机精度要求的机械零件就可以认为是大 00mm×800mm)、小的风电轮毂(球径3000mm左右)等,而且其孔系的位置度要求非常高(0.03mm左右),能应对其长宽高体量特征和测量精度的常规固定式坐标测量机已不多。以此类推,那么汽车白车身这一类工件的测量则不被认为是大工件,因为已经有成系列的 坐标测量机,同时由于是钣金成形及拼接件,其总体精度与机件相比还有一定的差距。

探头端接测试点长时间监测异常ZDS4的时序分析软件具备长时间统计功能,下班后设置好示波器,对数据采集仪的SPI总线时序连续监测一个晚上,第二天上班的时候,导出监测分析结果,如所示,一个晚上总共进行了72185次测量,其中有1347次是测量失败的,导致异常的原因是SPI的数据建立时间不满足后级芯片的时序要求。示波器自动保存了这1347份失败的测试报告,打第1345份测试报告,如所示,显示了当前建立时间为3.75ns(包含时序违规处截图),不满足后级芯片4ns建立时间的要求,而且历史出现 差的时序是3.5ns,时序是8.5ns,问题得以。